Levels of x86-64 Microarchitecture

In this article, we will discuss the types of x86-64 processors. In 2020, thanks to the collaboration of Intel, AMD, Red Hat, and SUSE, a division into levels of x86-64 microarchitecture features was created. This allowed for the definition of basic instruction sets available on the processor, which the compiler can refer to. Newer x86-64 processors have additional instructions, allowing the compiler to optimize the code, resulting in faster execution time at the cost of backward compatibility since code compiled for a newer level will not work on older processors that do not support these instructions.

What are the levels?

Each level of microarchitecture corresponds to a basic set of instructions available on the processor.

- Level 1, x86-64-v1 is the original x86-64 instruction set that debuted with AMD’s Athlon 64 in September 2003. The instruction sets/feature flags supported by this microarchitecture level include:

CMOV, CX8, FPU, FXSR, MMX, OSFXSR, SCE, SSE, SSE2 - Level 2, x86-64-v2, corresponds to Intel Nehalem (2009) and AMD Bulldozer (2010) processors and newer. It includes additional SSE3 + SSE4 instructions. The instruction sets/feature flags supported by this microarchitecture level include:

all from the previous microarchitecture plusCMPXCHG16B, LAHF-SAHF, POPCNT, SSE3, SSE4_1, SSE4_2, SSSE3 - Level 3, x86-64-v3, corresponds to Intel Haswell (2013) or AMD Excavator (2015) processors and newer. This instruction set adds AVX2, which introduces 256-bit registers for SIMD operations (instead of loading, operating, storing, and looping). This allows for fast operations on data represented in large arrays, such as matrices, vectors, etc. The instruction sets/feature flags supported by this microarchitecture level include:

all from the previous microarchitecture plusAVX, AVX2, BMI1, BMI2, F16C, FMA, LZCNT, MOVBE, OSXSAVE - Level 4, x86-64-v4, corresponds to processors supporting AVX512. AVX512 introduces SIMD instructions for new 512-bit registers. The instruction sets/feature flags supported by this microarchitecture level include:

all from the previous microarchitecture plusAVX512F, AVX512BW, AVX512CD, AVX512DQ, AVX512VL

Detailed information on the division of microprocessors into specific levels can be found here.

What is the benefit of choosing a specific microprocessor architecture?

KVM has the ability to pass instruction sets to the virtual processor in a VM, masking some of the hypervisor’s instruction sets from the virtual server.

If you have a specific application or operating system that requires a specific instruction set to function, you can specify the microarchitecture level that the virtualizer should emulate when creating a virtual server.

This can also be useful if migrating from VMware and the migrated operating system fails to boot because the original VMware environment had a host with a different microarchitecture. Specifying a microprocessor architecture identical to that on the source environment resolves this issue.

How to Choose or Change the Processor Architecture?

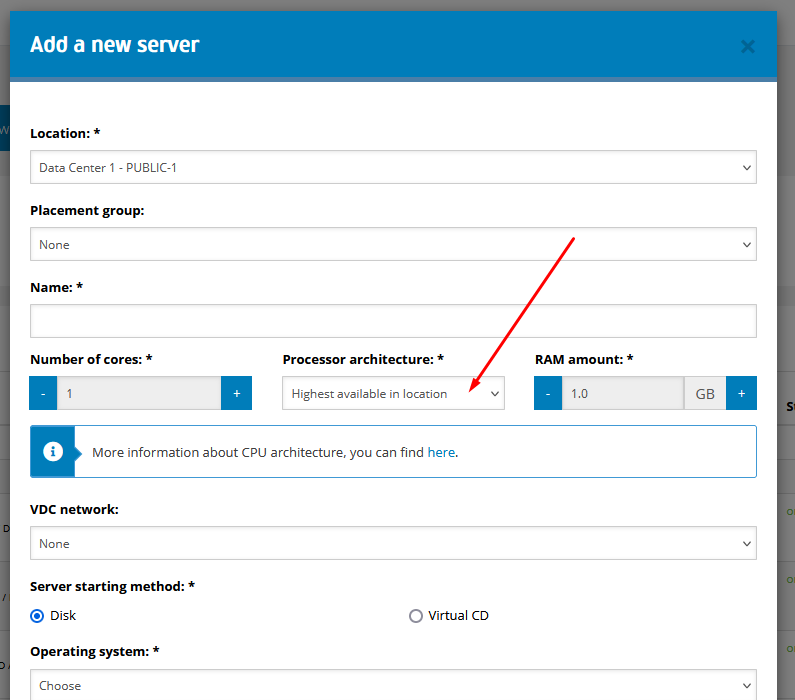

When creating a server or migrating from VMware, simply select the architecture on the server configuration form.

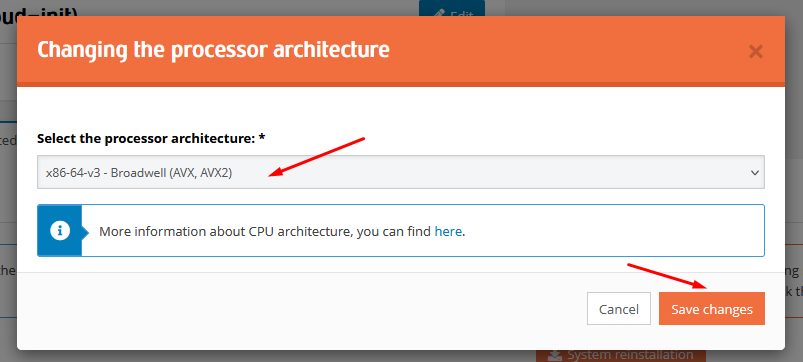

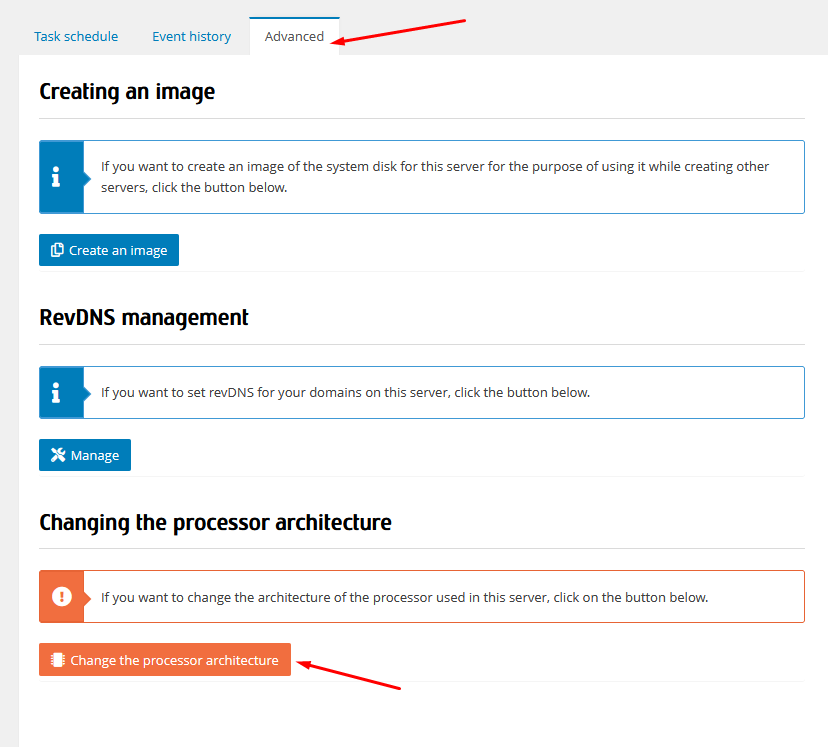

To change the processor architecture on an existing server, we first need to shut it down. Then, in the detailed view of this server, select the “Advanced” tab, and click on the “Change Processor Architecture” button.

In the window that appears, we can choose the architecture we need and then confirm our choice by clicking the “Save Changes” button.